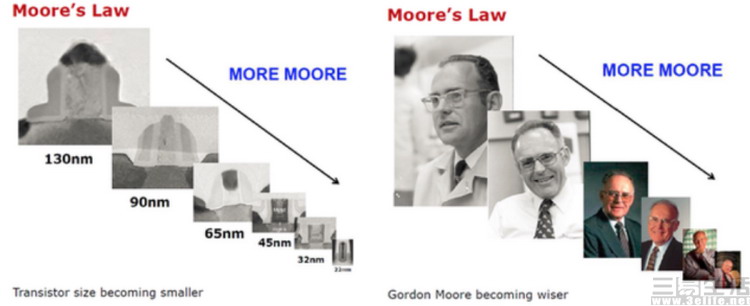

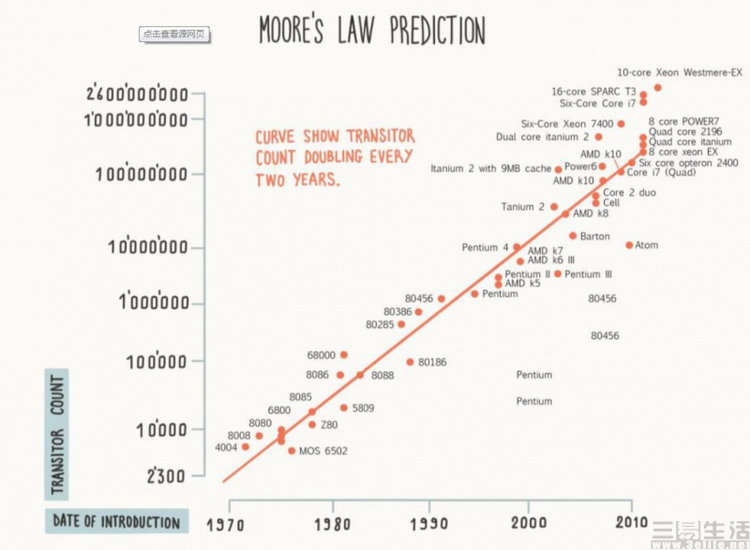

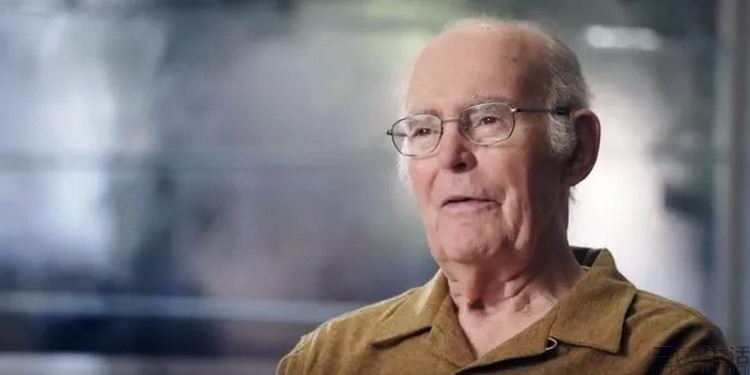

1965年4月19日,时任仙童半导体联合创始人的戈登·摩尔,在《电子学》杂志上发表了一篇行业分析文章《让集成电路填满更多的元件》。在这篇文章中,摩尔根据自己对半导体技术的理解大胆的提出了一个推断,即“在最小成本的前提下,集成电路所含有的元件数量大约每年便能增加一倍(原文:The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ,引自Intel官网)。”

是的,这就是大名鼎鼎的“摩尔定律”。对于我们三易生活的读者来说,可能知道我们早就对“摩尔定律”近年来在半导体行业中不断被扭曲异化的过程,以及它为何不会“过时”做出过详细的分析。只不过当时的我们主要是将矛头,对准了厂商篡改“摩尔定律”原文的行为本身,以及PC行业跑分软件在其中所扮演的角色,而对于半导体工业本身有些龌龊事却并未提及。

然而就在近日,TomsHardware撰稿人,行业分析师Arne Verheyde却以一篇文章有史以来最彻底的“捅穿”了半导体制造业的这层窗户纸。在这篇文章中,他直言不讳地说道,“这其中的大部分都是营销游戏(much of this is just that, marketing games)。”

早在几十年前,制程数字就已经不再可信了

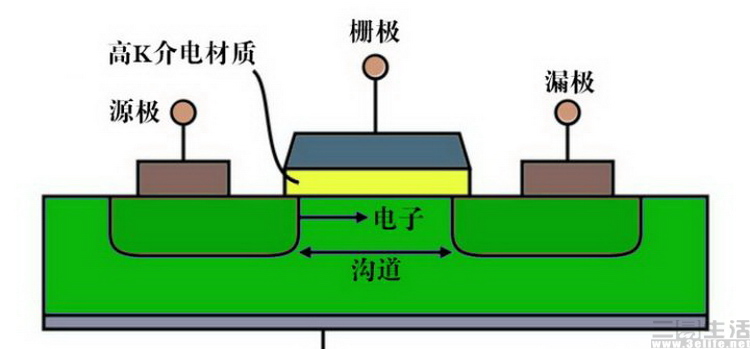

事实上,稍有关注科技领域的朋友,肯定不会对“制程”这个概念感到陌生。虽然可能不是所有人都知道制程的原本定义(晶体管沟道的宽度),但是“制程数字越小,制程就越先进,芯片的性能也就越高”却已经成为了消费者的一个共识。

可是,如果半导体制程的“数字”本身就不可信呢?如果我们一直以来所相信的7nm、14nm、28nm、甚至就连130nm都是虚假的呢?

正统的,学术意义上的“制程”,指的是晶体管沟道的宽度

按照Arne的说法,早在PC处理器刚开始频率竞争以来,半导体工业的“制程数字”其实就已经开始和实际的晶体管内部尺寸“脱钩”了。也就是说,最早的制程注水甚至要追溯到上个世纪90年代。那么问题就来了,如果制程数字实际上早就指的不是真正意义上的晶体管尺寸,那么它究竟意味着什么呢?

答案很简单,因为“制程数字”对于厂商而言,早就已经变成了单纯表示工艺新旧关系的代号;而对于不知情的媒体和消费者来说,大部分厂商每升级一次工艺就必定“进步”的制程数字,实际上也就成为了最好的商业宣传手段。

举例而言,2014年,当时台积电最先进的半导体制程工艺是“20nm”(这里的20nm只是一个代号,它不代表真正的工艺精度)。此时,半导体技术迎来了一个重大的变化,FinFET型晶体管的新设计诞生了,Intel准备将其用在自己的14nm工艺上,而台积电也从善如流,在他们的新生产线上导入了FinFET晶体管的新设计。

按照Arne的说法,FinFET是个好东西,因为它确实能够提高晶体管的性能,减少漏电。但问题就在于,台积电在升级新工艺的时候,仅仅只是导入了新的晶体管设计,并未进一步缩减晶体管的尺寸。那么大家觉得,此时(2015年)台积电的新工艺应该叫什么名字?是“20nm FinFET”吗?

并不,因为台积电最终决定将他们的新工艺命名为“16nm”。客观来说,虽然新工艺的确算是换代,也的确提高了生产出的芯片的性能,但是它的精度本身并未进步。而这实际上也就意味着,台积电所谓的“16nm”,其实应该理解为“比所谓的20nm更新一代的工艺”的意思。就好像现在的7nm工艺,指的其实也只是“比此前自称10nm的工艺更新一代的技术”一样。而至于它真正的晶体管尺寸级别到底是7nm还是10nm,还是其更大,这就只有厂商自己才能说得清楚了。

当制程成为宣传手段,它的“水分”也就越来越大

如果说,半导体厂商仅仅是把这些“制程数字”用于内部不同工艺之间方便管理、方便识别新旧关系的一种“代号”,那么我们顶多只能责备厂商不够诚实。但问题就在于,他们不仅仅是在内部“胡扯”半导体制程的“数字”,甚至还将这种谎言变成了一个相互攀比的宣传手段,比的就是谁更敢吹,谁的谎扯得更大更圆。

就拿我们刚刚讲到的,台积电在实际晶体管密度并未上升的大前提下,将“20nm”的改进工艺命名为“16nm”这件事来说。根据前几年另外一些渠道传出的消息称,台积电之所以敢这么做,纯粹也是因为被隔壁的三星“抢了风头”。因为三星的FinFET工艺同样没有带来实际晶体管密度的大幅上涨,但是他们却将新工艺抢先命名为了“14nm”,这导致当时台积电在营销上陷入被动,不得不也跟风“吹水”。

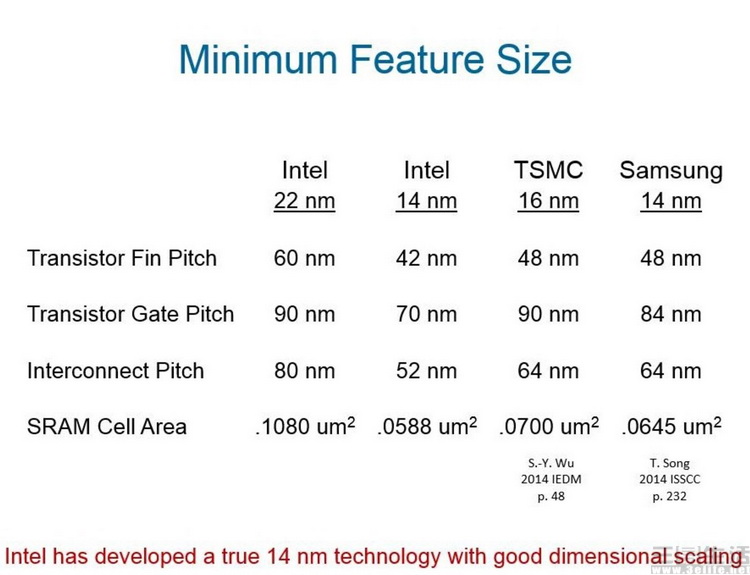

从当时一份公开的半导体工艺尺寸统计表中我们可以看到,在真正能够衡量晶体管制造工艺的栅极距 (Gate Pitch)、鳍片间距 (Fin pPitch)、金属栅距 (Metal Pitch)等指标上,无论是台积电的16nm还是三星的14nm,都与Intel后来推出的“真正”14nm工艺相去甚远,甚至前两者的新工艺在某些指标上仅与Intel的22nm老制程相当,也相当于进一步坐实了“制程数字造假”的说法。

而台积电和三星两家也很清楚,他们的半导体制程数字根本就经不起业内人士的推敲。比如在2019年的Hotchips芯片技术大会上,台积电技术研究副总经理黄汉森就主动和公开的承认了制程数字“造假”行为。用他的原话来说,“制程节点已经变成了一种营销游戏,与科技本身的特性没什么关系。”

新的制程衡量方式,或将重现摩尔定律的荣光

很显然,对于当今的半导体芯片制造业来说,这种“制程造假”的行为不仅由来已久,而且其危害之大也涉及到了行业的方方面面。对于上游企业来说,制程造假使得无晶圆芯片设计公司(比如AMD、NVIDIA、高通、联发科等)和芯片代工厂之间实际上形成了信息不对称局面,不仅加重了行业隔阂,有时候甚至也会导致产品制造出现问题,造成减产、延迟发布,或是性能不佳等后果。而对于大部分消费者来说,盲目相信“制程数字”也会使得大家无法客观认识到芯片之间真正的性能或是技术差异水平。

比如说,根据中信证券研究院在2019年公布的一份半导体工艺指标比较表就不难发现,如今各家最新的半导体制程工艺中,Intel“标称10nm”的工艺实际上在很多方面都与三星和台积电“标称7nm”的指标完全相同,甚至还要远好于台积电的第一代7nm工艺。但假使你对一位普通消费者说,其实Intel的10nm和其他家的7nm完全一样,这显然很难令一般人信服。毕竟,一方面来说不是人人都能看得懂艰深复杂的工业指标表格,而另一方面来说,老旧的,如今已经错误百出的“制程数字”理念早已深入人心。

正因为如此,Intel在2017年提出了一个全新的指标用于描述每一代制程工艺真正的晶体管制造水平。而这个指标近日在Arne Verheyde的文章中得到了进一步的阐释,这就是逻辑晶体管密度,单位MTr/mm²(百万晶体管每平方毫米)。

-page-019.jpg)

与各家标准都有所不同的“制程数字”相比,逻辑晶体管密度衡量发抛弃了那些出于商业私心的宣传成分,重新以纯粹的,晶圆上的晶体管密集程度来衡量不同制程之间的优劣。按照这一衡量方法,Intel现在的10nm+制程实际上可以做到每平方毫米1亿个晶体管,也就是100MTr/mm²,作为对比,台积电公布的“7nm EUV”制程晶体管密度为每平方毫米9000万个,也就是90MTr/mm²。不难看出,实际上台积电最先进的7nm制程,在半导体制造水准上反而是弱于竞争对手的“10nm+”的。这也就再一次证实了,这些年来的制程数字造假,究竟有多严重、有多误导人。

不仅如此,Arne Verheyde还在他的文章里进一步给出了更多Intel与台积电已知的制程晶体管密度数据。其中Intel的7nm晶体管密度为200~240MTr/mm²,而台积电目前刚刚投产不久的“5nm”制程仅有170MTr/mm²的水准;在台积电已经公布的“3nm”制程,晶体管密度为290MTr/mm²,作为对比,Intel这边的5nm则将会达到400~480MTr/mm²的水准。换句话说,届时Intel“上一代”的制程,在制造水准上就相当于台积电“下一代”工艺的1.5倍甚至更高。

当然,我们可以说台积电有点牛皮吹得太大收不住了。但是反过来说,当业界的其他竞争对手都在制程数字上灌水、吹牛的时候,为什么Intel却一直苦苦地坚持自己的命名规范,不把把14nm+++改叫做11nm,而且还非要追求每次制程换代必须带来100%的晶体管密度提升呢?

原因或许简单,因为现在还在世,91岁高龄的戈登·摩尔老前辈正是Intel的创始人之一。

【本文图片来自网络】